原理图输出之后的PCB设计部分 PCB设计过程中也对原理上会有反馈,比如调整引脚等

从原理图到PCB,器件及封装的对应

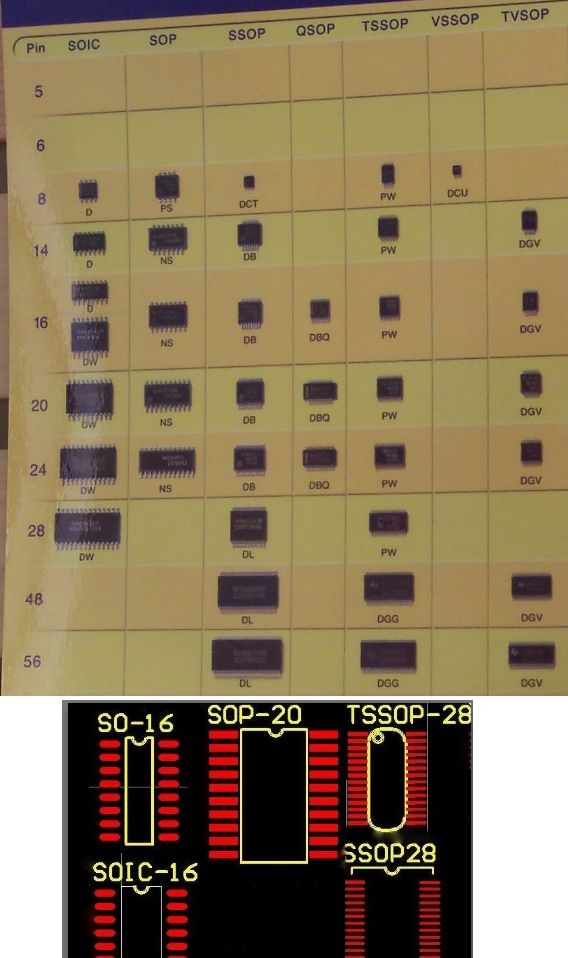

Orcad或Protel 生成netlist ERC检查!检查有无重复编号的,没有连上的等 先编好号,虽然是简单的编号,到PCB中之后再对应就麻烦了 采用自动编号方便和比较保险,虽然有些地方未必如意(可选择单个页面或者整个项目) 对整个活动项目操作,先采用一定范围的编号,这样可保证没有重复的 然后再次重新编号,这样就连续了 网络标号的注意 最好不要同时采用D1和d01 最好网络和编号不要用相同名称 自己制做元件符号 新建Schematic Library Document,制作完元件后,要加入自己的ddb,然后就可以调用该lib中的元件了 可以把该.lib命名为自己想要的名称 可以在该lib中制作多个元件,注意放引脚时连接头在外 可以重命名元件 找到元件的数据手册,看其中的元件符号 引脚编号是关键的 一些三极管,一般数据手册中1 2 3编号和常规封装中的是对应的,但可能和功能性引脚不对应,这可以在PCB中更改引脚顺序,更方便的是做一个元件,把编号改过来 编号不对应, 单行annotation 多行 text frame 我sheet设计出现Protel99:Duplicate Sheet Numbers 错误 document option–oganization中sheet no改成不同的编号即可 PP快捷键放置元件 常规元件和元件库 先添加元件库 Miscellaneous Devices.ddb Protel DOS Schematic Libraries.ddb 其中包含许多.lib Protel Dos Schematic 4000 Cmos .Lib (40.系列CMOS管集成块元件库) Protel Dos Schematic Analog Digital.Lib(模拟数字式集成块元件库)AD系列 DAC系列 HD系列 MC系列 Protel Dos Schematic Comparator.Lib(比较放大器元件库) Protel Dos Shcematic Intel.Lib(INTEL公司生产的80系列CPU集成块元件库) Protel Dos Schematic Linear.lib(线性元件库) Protel Dos Schemattic Memory Devices.Lib(内存存储器元件库) Protel Dos Schematic SYnertek.Lib(SY系列集成块元件库) Protes Dos Schematic Motorlla.Lib(摩托罗拉公司生产的元件库) Protes Dos Schematic NEC.lib(NEC公司生产的集成块元件库) Protes Dos Schematic Operationel Amplifers.lib(运算放大器元件库) Protes Dos Schematic TTL.Lib(晶体管集成块元件库 74系列) Protel Dos Schematic Voltage Regulator.lib(电压调整集成块元件库) Protes Dos Schematic Zilog.Lib(齐格格公司生产的Z80系列CPU集成块元件库) part1、2必须在制作原理图符号时 标号代替连线简介 放标号 也好比连线一样 会出现一个黑点 只有黑点连上才连上 放置元件在鼠标上时按TAB键更改属性 按空格逆时针旋转90度 选中的只按delete无法删除,需要按ctrl+delete 选中的需要在编辑中选择deselet-all取消选中 Protel99:Duplicate Sheet Numbers是什么错误? 是sheet编号重复。 打开SCH图, Document options中,单击organization标签,在下面的sheet NO.里面填好标号 封装温故 SOP-14即SO-14 SOP means Small outline package . QFP QFP means Quad Flat Package. TQFP方形扁平 正方形 Thin+ QFP 要密一些 LQFP 长方形 QFN无引脚封装 BGA should be the highest package in these package

要从原理图走向实际的板子,就需要和实际元件结合,选择合适的封装 采用标准封装 或者自己根据实际元件自己做封装 一定熟悉尺寸了 封装中的尺寸都是采用英制,比如AXIAL0.3中0.3是0.3英寸,.1/.2是0.1英寸和0.2英寸,0805是0.8英寸*0.5英寸 因此知道英寸与公制的换算比例就可感知具体尺寸 1英寸=2.54cm-=25.4mm=1000mil 有的自己不确定的可以在PCB中调出元件后自己测量测量,report中测量尺寸工具 常规插孔封装中引脚间距多为100mil,0.1in*25.4mm=2.54mm 元件名称及其封装 电阻 RES1是波浪形的电阻 RES2是矩形的电阻; 封装 包括电感在内的无极性双端类都是AXIAL0.3-1.0 AXIAL0.3-AXIAL0.7 其中0.4-0.7指电阻的长度,一般用AXIAL0.4,0.4是0.4英寸,是25.4*0.4mm,是400mil,大约10mm 贴片 片状黑色 0603表示的是封装尺寸 与具体阻值没有关系,但封装尺寸与功率有关通常来说如下: 0201 1/20W 0402 1/16W 0603 1/10W 0805 1/8W 1206 1/4W 电阻已经普遍用贴片电阻了 可变电阻 RES3是波浪形的滑动变阻器 RES4是矩形的滑动变阻器 (中间一个斜箭头); 三端 POT1 POT2 封装VR1-5 VR5和VR-5相同 电容 无极性电容 CAP是无极性电容,两道平行;RAD0.1-0.4 0402 0603 0805 1206 1210 1812 2225 有极性电容(电解电容) CAPACITOR 一道弯曲;CAPACITOR POL是极性电容,一道直一道弯曲,并在直的旁边标有正号; ELECTRO1大电容,一道为矩形块,一道为直线,并在矩形块附近标有正号;ELECTRO2同上个,但是一道直线粗; RB.2/.4 或RB.4/.8 是整体的,分别表示两脚间距或焊盘间距和圆筒外直径 一般<100uF用RB.1/.2,100uF-470uF用RB.2/.4,>470uF用RB.3/.6 贴片 片状 圆柱状 无极性电容下述两类封装最为常见,即0805、0603; 电解电容平时用的最多的为铝电解电容,由于其电解质为铝,所以其温度稳定性以及精度都不是很高,而贴片元件由于其紧贴电路版,所以要求温度稳定性要高,所以贴片电容以钽电容为多,根据其耐压不同,贴片电容又可分为A、B、C、D四个系列,具体分类如下: 类型 封装形式 耐压 A 3216 10V B 3528 16V C 6032 25V D 7343 35V 电容也多用贴片电容了,除了电源处的大电容 一般<100uF用RB.1/.2,100uF-470uF 用RB.2/.4,>470uF用RB.3/.6 电感 INDUCTOR无极性双端类都是AXIAL0.3-1.0 二极管 DIODE0.4 0.7 diode-0.4(小功率)diode-0.7(大功率)0.4-0.7指二极管长短,一般用DIODE0.4 发光二极管 LED ;RB.1/.2 ? 贴片 根据所承受电流的的限度,封装形式大致分为两类,小电流型(如1N4148)封装为1206,大电流型(如IN4007)暂没有具体封装形式,只能给出具体尺寸:5.5 X 3 X 0.5 二极管也多用贴片了 发光二极管仍用插孔的 LED封装引脚是A和K,即anode正极和cathode负极 三极管 NPN PNP 封装 对于晶体管,看它的外形及功率,TO-xxx(TO-3,TO-5),大功率的晶体管,就用TO—3,中功率的晶体管,如果是扁平的,就用TO-220,如果是金属壳的,就用TO-66,小功率的晶体管,就用TO-5,TO-46,TO-92A等都可以,反正它的管脚也长,弯一下也可以 TO92A 是半圆形的并且三个引脚这样分布:半圆直径两边分布两个,半圆顶部分布一个; TO-92A是多边形封装(形状:在一个矩形下面(比如说)的长边分别向下折120度,少许延伸后又水平封住)并且三个点是散开分布的、不是在一条直线上 T092B 半圆形的 并且三脚在一条直线上 TO-92B TO220 带翅的 场效应管FET和晶体管一样? 贴片 三端片式 一端一个引脚一端两个引脚 SOT-23 小功率三极管 功耗小于300mW SOT-89 功耗在300mW-2W之间 SOT-252 用于功耗在2W-50W较大功率器件 三极管也多用贴片的了 TO92A为一个圆形的,TO-92A为一个多边形的 芯片 SIP(single in-line package) DIP(dual in-line package) DIP-20封装相邻100mil,两排之间300mil DIP-22封装相邻100mil,两排之间400mil DIP-24 DIP-40封装相邻100mil,两排之间600mil 贴片 SOP small outline package 对应DIP QUAD quad packs四面封装 QUAD64 QFP四面封装 方形扁平封装 QFP-52两脚之间39mil,各种引脚数的都不相同 DIP40和DIP-40可以说相同 晶振 CRYSTAL符号为两道中间是小矩形;XTAL1 晶振仍插口 整流桥 FLY4 对Bridge 插针 20PIN CON20 header 14 ? 开关 按钮 SW-PB为双端上有按钮的的开关 保险丝FUSE1 中间一道 FUSE2 中间弯曲 继电器 RELAY-DPDT RELAY-DPST RELAY-SPDT RELAY-SPST 电源和地不用VCC和GND 而是布线中的那个地形状,出来是电源,属性中可以根据需要更改 电源稳压块7805 79系列等 VOLTREG 封装TO126H TO126V 重要注意事项 对于三端器件,比如三极管,7805,一定要具体对应一下器件手册中的封装引脚和实际封装中是否对应,有的需要在原理图中通过自己制作元件来更改引脚次序,或者在PCB中更改焊盘的编号,而前者更好 自做封装 根据手册、资料说明做封装时要注意 PCB中底层的本身看去就是底视图 底视图看的做封装轮廓线就放成底部的还不行,到PCB中轮廓是底层的但是还是视为顶层的,所以一定还要转化为顶层的封装才行 尺寸的测量 在画封装时,引脚的间距和长度,固定两脚的尺寸和相对引脚的距离 对于贴片,在PCBLIB中防止Pad,然后选择在Top层,hole size=0,可更改长宽,可选择形状,圆形了矩形了等 自做封装 查找相关资料 或测量实物做 先轮廓 然后相对定位点 然后引脚之间相关位置或者先引脚之间 然后找轮廓与其相对关系 阵列粘贴 paste中 special paste 选择个数,选择变化间隔,比如相邻递增是1,可使用递减-1;选择x,y间距 关于点击后粘贴的准确位置,还不怎么好确定,可以就采用移动和确定的部分重合的办法 解决了一个个放置和计算坐标的麻烦 设置参考点 便于将来调用时不偏离鼠标太远 protel中用component wizard制作LQFP-48封装 component wizard—> quad packs —> pad 尺寸 长2mm,宽0.27mm —>第一个Pad可选择矩形,其他圆形 —>相对距离:Pad间距 0.5mm,最后一个pad到邻边的距离2mm —->数目12pins 封装注意: 三极管封装十分小心,即便它一个公司的也会出现不一致 其他 后期可以由PCB生成PCB封装库 1inch=25.4mm 补充 TQFP似乎不同引脚数的尺寸不同,比如某个TQFP-44引脚间距是0.8,可能其他某个引脚数的是0.5;记得以前曾经在这个封装上遇到封装做错的情况,要看准器件封装说明才是

布局

把已知固定的部分确定好,尤其结构部分

面 连接器位置,线序 特殊高度要求 比如连接器的位置,按键,指示灯 如果有结构设计者做好的结构图,导入之,导入时注意选择公制和缩放比例(一般导入全比例的结构图不采用缩放比例) 根据每面限制的高度和操作的适宜性确定那面放什么东西 确定有特殊限制的区域不能放什么 避免产生抵触 固定结构先锁定下来,防止过程中误动,在过程中意外移动时有所提醒 这是硬性问题 这是第一步 第一步没有做好 后面再改动就划不来了 最好能参照到实物 如果没有实物 也一定好好研究研究结构图 参考正面 反面 接插件通常对着后盖的 接插件 为了便于连接 有些接插件有固定的位置或固定的范围区域的 如果是第一次做 则不必考虑什么次序 但如果已有先例 则必须对应次序;自己做一套的话,也相互对应次序 还有指示灯问题 指示灯放在什么位置 便于看到 还有按键,便于操作 大的插孔式的和接插件放一面,贴片放置另一面 成功从AutoCAD导入关键 保证AutoCAD中是1:1 导入时protel中选择公制 metric protel安装protel99seservicepack6才有选择公制英制的选项 import as components将把图件视为元件外表导入,单击Import as primitives单选按钮将把各图件分别视为独立的基本图件。

- 弄清方位和相对关系,选定层面

从背面看还是正面看 导入dxf不需要autocad{ imperial 英制 metric 公制 import as componets/primitives} 那一层放高器件 插孔和贴片混合则把插孔安装在一面,不然双面装配太复杂 而贴片可以双面

- 弄清连接器位置和对应问题

尽量考虑利用现有的线束等

对结构的反馈

做产品过程中是结构和电气相互配合的 在布局过程中,发现不适合的地方,提出来对结构进行反馈,需要争取一些结构上有利于电气的就争取

布局模块化

结构适应性加模拟数字分开,相互调和 先布可以确定的 已确定的可以先成块布线 走出去 引出来:引线多的优先成束走出 难走出的优先成束走出 也优先考虑考虑电源 同类不同面减小面积不行 没办法才异类重叠 不必强求全面一面插孔一面贴片 在空间有限的情况下一面贴片一面插件已经不重要了 芯片电源地滤波根据情况灵活放在入口,不一定死板跨在两边 最好空间足够大,模块分明 先把主要的集成芯片挑出来放置中央 把电源、开关、指示灯等挑出来,电源放在一端(电源入口处设滤波去耦电容),开关也放在边沿 把一些其他特殊元件,发热元件和热敏元件挑出来,热源外置/单置/高置,怕热、热敏元件远离热源,引导散热 按信号流向布置,就近布置,避免迂回穿插 芯片不能左右上下翻转 粘贴时选择特殊粘贴,选择保留网络就可以 移动之前确保按一下取消选中以防有已选中的 尺寸问题可以英制和公制切换view-toggle units 切换成公制便于自己估量 但有时还是使用英制的好,因为要用到100mil这样的数据,转换成公制不是整数了 前面布局时也要兼顾考虑一下电源和地 不要等到最后电源、地非常难走通 一个好的布局会有好的布线效果 在限制较大的条件下,一个坏的布局甚至可能会难以布通,如果再重新洗牌,算来真是事倍功半了

特殊考虑因素

散热设计要求 5.2.1 高热器件应考虑放于出风口或利于对流的位置 PCB 在布局中考虑将高热器件放于出风口或利于对流的位置。 5.2.2 较高的元件应考虑放于出风口,且不阻挡风路 5.2.3 散热器的放置应考虑利于对流 5.2.4 温度敏感器械件应考虑远离热源 对于自身温升高于30℃的热源,一般要求: a. 在风冷条件下,电解电容等温度敏感器件离热源距离要求大于或等于2.5mm; b. 自然冷条件下,电解电容等温度敏感器件离热源距离要求大于或等于4.0mm。 若因为空间的原因不能达到要求距离,则应通过温度测试保证温度敏感器件的温升在降额 范围内。 5.2.5 大面积铜箔要求用隔热带与焊盘相连 为了保证透锡良好,在大面积铜箔上的元件的焊盘要求用隔热带与焊盘相连,对于需过5A 以上大电流的焊盘不能采用隔热焊盘,如图所示: 焊盘两端走线均匀 或热容量相当 焊盘与铜箔间以”米”字或”十”字形连接 5.2.6 过回流焊的0805 以及0805 以下片式元件两端焊盘的散热对称性 为了避免器件过回流焊后出现偏位、立碑现象,地回流焊的0805 以及0805 以下片式元件 两端焊盘应保证散热对称性,焊盘与印制导线的连接部宽度不应大于0.3mm(对于不对称焊盘), 如图1 所示。 5.2.7 高热器件的安装方式及是否考虑带散热器 确定高热器件的安装方式易于操作和焊接,原则上当元器件的发热密度超过0.4W/cm3,单 靠元器件的引线腿及元器件本身不足充分散热,应采用散热网、汇流条等措施来提高过电流能 力,汇流条的支脚应采用多点连接,尽可能采用铆接后过波峰焊或直接过波峰焊接,以利于装 配、焊接;对于较长的汇流条的使用,应考虑过波峰时受热汇流条与PCB 热膨胀系数不匹配造 成的PCB 变形。 为了保证搪锡易于操作,锡道宽度应不大于等于2.0mm,锡道边缘间距大于1.5mm。

尝试布线和粗略布线 进一步验证布局

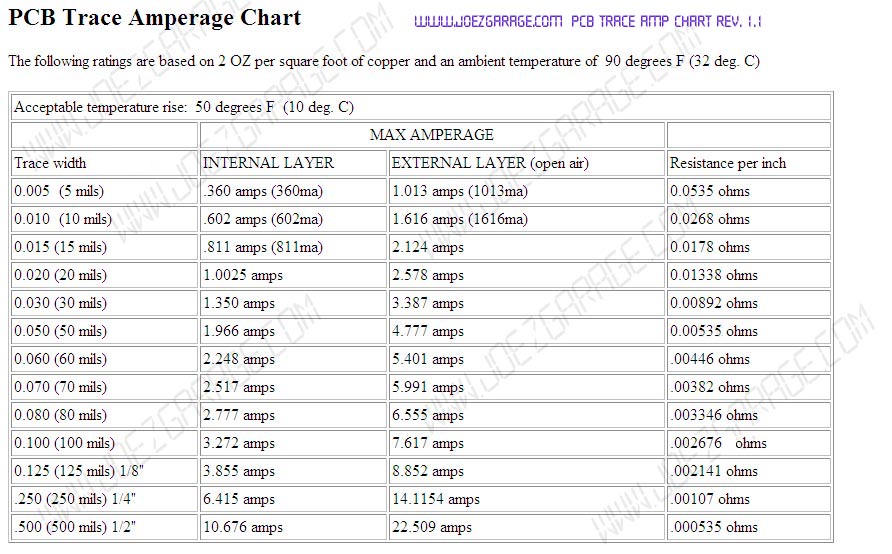

通过尝试布线,进一步确定布局情况如何 有的布局之后布线是件很容易的事情,空间充足,相互制约性较小;有的则因为条件的限制而十分困难,相互制约的太多了 先弄清常规走线方向 顺序走线,忌迂回穿插 走线简洁,短,特别低电平高阻抗部分平行线效应于长度成正比 避免成环,减少天线效应,电磁干扰 一点接地,地线干扰,高频大面积地 粗细适当,电源、地线、大电源线要保证宽度 低电平、高阻抗线应远离电源线、高电平线 1inch=1000mil=2.54cm=25.4mm —————————— 布线宽度和安全间距 一般安装密度不大的印制板,印制导线宽度不小于0.5mm为宜,手工制作的板子应不小于0.8mm 电源线要粗 可事先把电源线设置粗些,也可以最后再处理,但一定不要忘了 芯片处的常常较细 一般走线常用12mil 电源线常用40mil 50mil 有的也用20 30mil等 有的芯片引脚细密,引脚本身12mil的可以11mil走出来 安全间距14mil,覆铜板时18mil,加泪滴时22mil 后来我一般走线用15mil 安全间距15mil 一些模拟信号也适当比数字信号粗一些,比如声音,视频的 ———————————————— 覆铜板的宽度默认是10mil,应改成20mil 每层走线方向保持一致既美观也使布线有章可循 确定哪面那个方向 双面垂直 成股的排着走 有的在另一面可以走的,但为了保持单面走线的一致性和双面的垂直美观标准,也打到另一面走 安全间距十分重要,是保证布线距离从而保证板子可用性和可靠性的关键所在 布线时在安全间距规则下走线,保证间距 覆铜板,补泪滴也一定要在安全间距前提下 rules中第一项就是安全间距-clearance ,一般10mil至少是要有的,一般12mil,能大一些就大一些,比如14mil,补泪滴、覆铜板可以选择在14mil前提下 常常要设置多项,对于一些像PIC主控芯片的元件,间距很小的,不能使用适用于整个board的间距,往往需设置为5mil,有的flash闪存的间距可能会还更小,设置需要设置为3mil 在布线这些元件时,要采用这些规则,不然布线不了,线走不过去 地的质量,放地过孔趋肤效应 电源走线也要先整体规划一下,先不管电源和地是不好的习惯,后面要花很大的功夫,先规划一下电源才好!!! 面积有限,走线不容易 电源也要先布线,有意识引导 芯片走出去再过孔分离 大电解电容焊盘加大,我加宽 长距离的还要注意单面单向 过孔不要距离焊盘过近,也不要放到焊盘上,放在焊盘上手工焊接没有问题,SMT就基本是全军覆没。除非把VIA做的很小,并做塞孔处理。不然就会漏锡,虚焊。 螺丝孔附近注意减少导致短路的因素 如果我自己设计电路,那肯定根据布线结果最终摆放CPU管教 电源线50 40 30 (也包括一些名称不为电源的电源区的线)一些模拟线 25 一般线 先看15 不行可12 安全间距先用14 可增加要求看隐患 覆铜时18 过孔默认为50 28,有点大,可以改为30,18 netclass 设立net类,比如power,address,highVoltage等,然后施加不同的布线策略 建立region规则,解决芯片周围走线细的问题 设置涂漆规则 选中tending或者规则设置负值超过半径 在规则中,上面的优先级大于下面的,如果一条规则没有作用到,调整一下优先级可能就行了 推挤:interactive routing –>push obstacle 原avoid

PCB走线宽度

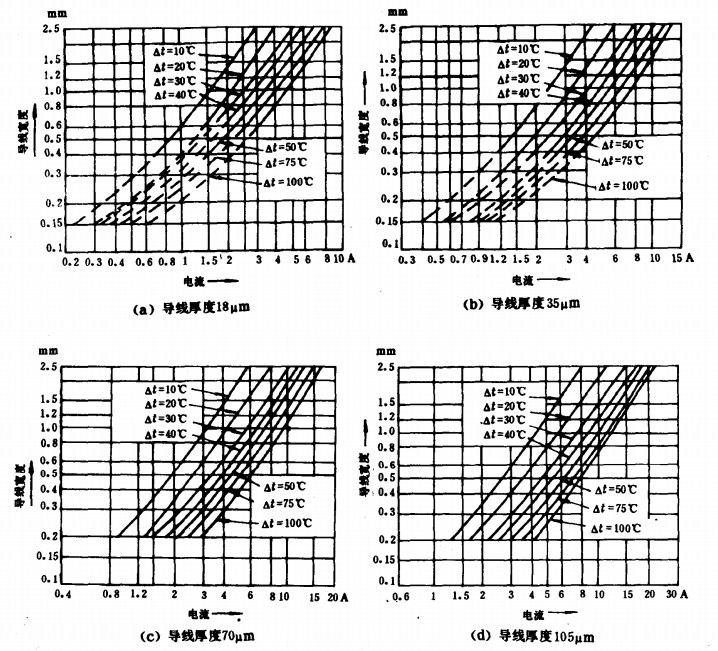

在做带强电的项目时候这个问题又得重新审视了,如果空间允许当然都是越宽越好,数字电路的比较清楚了,常用的 10mil,12mil,14mil,15mil等,据称0.2mm到0.3mm即可,而10mil就是0.254mm了;电源常用的比如 30mil,40mil,50mil 强电呢?220V电压,大电流呢,线宽多少,间距多少? 一些资料: //间距1.5mm,可耐压300V 铜箔厚度→ 70um 50um 35um 铜箔宽度↓ 2.50mm 6.00A 5.10A 4.50A 2.00mm 5.10A 4.30A 4.00A 1.50mm 4.20A 3.50A 3.20A 1.20mm 3.60A 3.00A 2.70A 1.00mm 3.20A 2.60A 2.30A 0.80mm 2.80A 2.40A 2.00A 0.60mm 2.30A 1.90A 1.60A 0.50mm 2.00A 1.70A 1.35A 0.40mm 1.70A 1.35A 1.10A 0.30mm 1.30A 1.10A 0.80A 0.20mm 0.90A 0.70A 0.55A 0.15mm 0.70A 0.50A 0.20A 3.2载流量 印制导线的载流量主要受印制电路板最高工作韫度的限制,也受短时间的大电流和热膨胀造成的 机械应力等因素的影响。 温度的数值取决于下列诸因素: t 电气功耗:单位面积上的功耗及其在印翻电路板上的分布情况; b 印制电路板的尺寸和材料,金属量及其分布情况} c 印制电路板装方式:水平安装或垂直安装,离相部部件或机柜边框的距离等; d 印制电路板表面的热辐射及其和邻近部件的温差,以及它们的绝对温度; e. 安装器件的热传导; f 热量对流方式:自然冷却或强制玲却。 以上诸因素是相互关连的。在大多数情况下根据具体情况正确估算就能满足要求。在重要的地方, 导线的载流量必须按实际使用情况测定。 3 2 1连续电流 3 2 1 1单面板的热耗 对于以铜为导电材料.标称厚度为1.6~3 2mm的单面印制电路板,不同宽度和常用厚度的印制 导线的温升与电流之间的关系(不包括附加镀层的影响),如图8所示。

另外有一些国外的网站在线计算,比如http://www.pcbco.com.au/tracecalc.html

极其重要的地!

一定跨再芯片本身的电源和地上,不能因为布线时先隐藏了地导致最终转了很大弯子回来 虽然布线时隐藏地 也一定要实现注意地 芯片加的电容是否真的电源地圈子小,为了保障这一点,还是放到另一面 并且地作为电源负极,也要保证地的宽度 铺地不仅要铺通还要保证质量! 能粗的地方尽量粗 能打过孔的地方尽量多打过孔 过孔不应放在中间,应该放在双面重叠的边沿,趋肤效应!!! 先固定的部分 然后调整CPU 电源 地要求严格 电源一定要尽量粗,多打过孔 地铺的不要影响比较大,比如造成视频信号不好等 单面单向走线的是与非 单面一致性是一种效果 但有太严格处处单面单向则显得死板,有时确实不单面单向弯曲布线更显得美观 只要有空间,能粗就尽量粗 先覆铜板看联通了多少, 可安全间距18mil 把一些无网络的散热片加地 贴片接插件的固定脚接地可加强固定 没联通的,有的添加一些过孔,有的需要引线引出来,细密芯片的地往往需要专门引出来,铺地时由于安全间距不会铺到 如果事先对地有兼顾则好弄一些 如果出现孤岛现象得想法弄出来 布通还不行,还得保证质量,看宽度是否可以,如果某一大片就靠一个很细的连过去,就不可靠 在一些宽裕空闲的地方多放一些地过孔有利于加强接地效果 在布线中先把GND网络隐藏了,最后用覆铜板铺地,铺覆铜板时电气上选择地网络 如何先隐藏GND网络的飞线?在左侧网络列表中选择GND,双击,然后属性中选择隐藏即可 如何覆铜板? 覆铜板之前一定要有个前提:必须在适当的安全间距下覆铜板,否则将和正常走线距离很近很近,没有间隙! 安全间距14mil以上好,14,15,18了 具体覆盖铜板,place中polygon(多边形) plane,然后沿禁止布线框画覆铜板的区域 注意选择GND网络 初始默认的设置值是8mil 8mil,更改为20mil 18mil则显示的是比较大一些的网格,如果喜欢细密的,就采用8mil的 覆铜板也未必把地就连成了一体!常常出现一些孤岛,地网络分成多个子网络 这时需要在覆铜板上放置一些过孔将正反的连通,甚至反过来更改一些走线布局来将地连接在一起 知道最后运行DRC检查地也连成了一体 可以说刚开始隐藏地是为了减少考虑的因素,不过从后来看,也不能完全不考虑地,免得造成那种特难出来的孤岛 覆铜板可以先删除,edit中delete,再重新放置,也可以先移出来然后重新移过去,rebuild 先覆盖铜板之后放地过孔是放在了覆铜板上了,但如果已有过孔后后覆铜板,则可能出现地过孔没有在覆铜板上!这时覆铜板时需要选择两个选项,让识别原来的网络 覆铜板后一定要先隐藏覆铜板(已经很熟悉了,右键 show/hide,或者tools-preferance)在安全间距前提下看一看刚才放的地过孔有没有触犯安全规则!因为刚才放的地过孔可能会与其他走线过近,很容易短路 这些小细小节都是在具体实践中经历的!! 有的小板子可能就不需要覆铜板了,采用较粗的地就行了 至于多层板则设置专门的地层 开始时画框,后来修改时可采用拉出来然后rebuild覆铜板 如果先放了地过孔,要通过选中两个选项让识别加到覆铜板上

走线间距 爬电间距 Creepage distances

参考: 交流电源进线,保险丝之前两线最小安全距离不小于6MM,两线与机壳或机内接地最小安全距离不小于8MM。 保险丝后的走线要求:零、火线最小爬电距离不小于3MM。 (3)高压区与低压区的最小爬电距离不小于8MM,不足8MM或等于8MM的。须开2MM的安全槽。 (4)高压区须有高压示警标识的丝印,即有感叹号在内的三角形符号;高压区须用丝印框住,框条丝印须不小于3MM宽。 (5)高压整流滤波的正负之间的最小安全距离不小于2MM。 — 1、 安全距离包括电气间隙(空间距离),爬电距离(沿面距离)和绝缘穿透距离。 2、 电气间隙:两相邻导体或一个导体与相邻电机壳表面的沿空气测量的最短距离。 3、 爬电距离:两相邻导体或一个导体与相邻电机壳表面的沿绝绝缘表面测量的最短距离。 4、 一次电路:一次电路是直接与交流电网电源连接的电路。 5、 二次电路:二次电路是不与一次电路直接连接,而是由位于设备内的变压器、变换器或等效的隔离装置或由电池供电的一种电路。

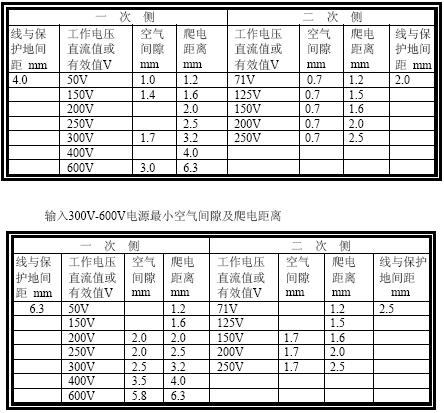

爬电距离一次侧线路之电气间隙尺寸要求,见表3及表4 二次侧线路之电气间隙尺寸要求见表5 但通常:一次侧交流部分:保险丝前L—N≥2.5mm,L.N PE(大地)≥2.5mm,保险丝装置之后可不做要求,但尽可能保持一定距离以避免发生短路损坏电源。 一次侧交流对直流部分≥2.0mm 一次侧直流地对大地≥2.5mm(一次侧浮接地对大地) 一次侧部分对二次侧部分≥4.0mm,跨接于一二次侧之间之元器件 二次侧部分之电隙间隙≥0.5mm即可 二次侧地对大地≥1.0mm即可 — 二.从 GB4943-2001 中 2.10 条款定义理解: 在 GB4943;2.10 条款中指出电气间隙的尺寸应使得进入设备的瞬态过电压和设备内部产生的峰值电压不能使其击穿。爬电距离的的尺寸应使得绝缘在给定的工作电压和污染等级下不会产生闪络或击穿(起痕)。由此可以看出,电气间隙和爬电距离的防范对象和考核目的不同。电气间隙防范的是瞬态过电压或峰值电压;而爬电距离是考核绝缘在给定的工作电压和污染等级下的耐受能力。 从对一次电路二次电路的名词定义可以看出,二次电路可能是安全可触及的,也可能是危险带电的;一个设备内可能同时存在一次电路和二次电路,例如预定与电网电源直接相连使用的电源适配器;一个设备也可能本身就是二次电路,例如采用一台发电机或电池供电的设备。在理解和区分一次电路和二次电路的基础上,也就理解标准中为什么二次电路中也有 对基本绝缘、附加绝缘、加强绝缘等的电气间隙的要求。 具体测量步骤步骤如下: 一)电气间隙的测量步骤: 确定工作电压峰值和有效值; 确定设备的供电电压和供电设施类别 ; 根据过电压类别来确定进入设备的瞬态过电压大小; 确定设备的污染等级(一般设备为污染等级 2); 确定电气间隙跨接的绝缘类型(功能绝缘、基本绝缘、附加绝缘、加强绝缘)。 二)确定爬电距离步骤 确定工作电压的有效值或直流值; 确定材料组别(根据相比漏电起痕指数,其划分为:Ⅰ组材料,Ⅱ组材料,Ⅲa 组材料, Ⅲb组材料。注:如不知道材料组别,假定材料为Ⅲb 组) 确定污染等级; 确定绝缘类型(功能绝缘、基本绝缘、附加绝缘、加强绝缘) 电气间隙、爬电距离的要求值: 电气间隙根据测量的工作电压及绝缘等级,查表(GB4943:2H 和 2J和 2K,60065-2001表:表 8 和表 9 和表10) 检索所需的电气间隙即可决定距离;作为电气间隙替代的方法, 4943 使用附录 G替换,60065-2001 使用附录 J 替换。 爬电距离根据工作电压、绝缘等级及材料组别,查表(GB4943 为表 2L,65-2001 中为表11)确定爬电距离数值,如工作电压数值在表两个电压范围之间时,需要使用内差法计算其爬电距离。 *GB 4943 中只有功能绝缘的电气间隙和爬电距离可以减小,但必须满足 标准 5.3.4 规定的高压或短路试验。 三.从 GB8898-2001 中 13 条款定义理解: 在 GB8898-001中 13 条款中电气间隙考虑的主要因素是工作电压,查图 9 来确定。(对和电压有效值在 220-250V 范围内的电网电源导电连接的零部件,这些数值等于 354V 峰值电压所对应的那些数值:基本绝缘 3.0mm ,加强绝缘 6.0mm)。 GB 8898-2001 其判定数值等于电气间隙,如满足下列三个条件,电气间隙和爬电距离 加强绝缘可减少 2mm,基本绝缘可减少 1mm。 1.这些爬电距离和电气间隙会受外力而减小,但它们不处在外壳的可触及导电零部件与危险带电零部件之间; 2.它们靠刚性结构保持不变; 3.它们的绝缘特性不会因设备内部产生的灰尘而受到严重影响。 *注意:但直接与电网电源连接的不同极性的零部件间的绝缘,爬电距离和电气间隙不允许减小。基本绝缘和附加绝缘即使不满足爬电距离和电气间隙的要求,只要短路该绝缘,设备仍满足标准要求,则是可以接受的(8898 中 4.3.1 条)。 四.关于 GB19212.1-2003 中 26 条款的理解。 自 2007 年3月 1 日开始实施的国家标准 GB19212.5-2006《一般用途隔离变压器的特殊要求》、GB19212.7-2006《一般用途安全隔离变压器的特殊要求》、GB19212.18-2006《开关型电源用变压器的特殊要求》。GB19212.1-2003 作为通用要求和试验,在 26 条款中电气间隙爬电距离的主要考虑因素为电压类别、污染等级,绝缘材料组别。对于采用浸渍、灌封或者使用粘结胶带覆盖绕组来进行隔离的变压器,如果能满足 GB/T16935.1-2007 的 4.1.1.2.1的试验,爬电距离可有有相应的减小值,但应当按适用的情况进行附加的试验(见 26.2 条 中 a),b),能通过相应的介电强度试验。 五.关于 GB15092.1-2003 中 20 条款的理解。 电气间隙的测量主要考虑因素额定电压、电压类别和污染等级,对基本绝缘、工作绝缘、附加绝缘、加强绝缘、三种断开状态分别加以说明,另外对于基本绝缘及附加绝缘有必要时可进行附录 M 脉冲电压试验以验证电气间隙经得起规定的瞬时过电压。 爬电距离的测量主要考虑因素为正常使用中预期会出现的电压,、污染等级、材料组别。对基本绝缘、工作绝缘、附加绝缘、加强绝缘、三种断开状态也分别加以说明 六.四份标准对测量路径的考虑。 一)X值的选取 1)GB4943,GB19212.1,GB15092.1 中从污染等级的角度规定了的 X宽度是相同的 污染等级 X宽度 1 0.25mm 2 1.0mm 3 1.5mm 注:如果涉及到的电气间隙小于 3mmm,则沟槽宽度 X最小可减小到该距离的1/3。 2)GB8898 对直接与电网电源连接的,X 值规定为 1.0mm。对不直接与电网电源连接的,且经过防灰尘和潮气侵入的封闭、包封或气密密封的设备、组件或元器件,X 值规定为0.25mm。如果涉及到的电气间隙(伴有相关的爬电距离)的要求小于 3mm,则沟槽宽度 X最小可减小到该距离的 1/3,但不小于 0.2mm。 二)电气间隙爬电距离的测量路径。 a)所考虑的路径包括一个具有任一深度而宽度≥Xmm的平行边沟槽。 b)所考虑的V形沟槽路径在 GB4943,GB8898,GB19212.1 包括内角角度,而宽度大于 Xmm。 在 GB15092.1 开关中路径包括宽度大于 Xmm,对角度没有作出相关要求。 c)所考虑的路径包括肋。 d)所考虑的路径包括两边沟槽宽度≥Xmm的一个非粘合接缝。 e)所考虑的路径包括一个扩展边的沟槽。 f)在螺钉头与槽壁之间的空隙太窄<Xmm,可不予考虑。 七.结束语。 在日常测量电气间隙爬电距离不同的人往往结论有差异,首先要注意是否引入了过多的人为误差,包括测试手段,测量时,一般使用卡尺\千分尺\塞规等,更进一步的手段有读数显微镜\投影法,甚至极精细情况下,有电镜等手段。根据以上四份标准的对比,还可以看出不同的标准对测量电气间隙,爬电距离考核角度、测量要求是有差异的。针对具体产品选用恰当的标准,具体情况具体分析这样才能保证结论的准确性。 — 我设计一个控制灯的收音机,在申请UL认证时PCB过不了4.8mm的安全爬电距离(低压电源电路部分与220V高压电路部分), PCB板的高压220v和低压5V的安全间距最小是多大 悬赏分:0 解决时间:2009-2-4 13:29 提问者:wenjie605 最佳答案 我对自己的要求是5MM我现在设计的家电控制PCB板都是在5MM (好像正规的220V和低压最小就是5MM) 要实在没办法相聚5MM那最少2.5MM是必须的 其实看环境的要是PCB工作的潮湿的环境那尽量距离大,相对的在干燥的环境稍微近点没关系 好多手机充电器上面的220V和输出的5V在PCB上间距只有2MM但是也可以正常使用(透露下还是NOKIA手机的充电器哦~) —–

其他

查看某一层的走线效果,options中 load netlist…时右键单击,然后选择add…,然后可以添加net等 PCB中手工调整网络 可以点击一个焊盘,然后advance中选择一个网络,便加入了相应网络并建立了飞线 主控芯片电源不从继电器引过来 怕继电器动作时电流变化引起主控芯片电源不稳定 过孔唾沫漆很有必要,防治过孔离焊盘过近导致短接 涂抹油漆增加可靠性 Protel换面自动添加过孔 按数字键盘* ,走线时按tab也可选择层操作,另外数字键盘 + -可快捷换层;这些以前还没怎么注意 解决过孔不良影响 1 过孔距离焊盘过近,焊接时候造成短路 2 焊接时焊锡流失 虚焊 解决办法 1 过孔放置不要距离焊盘过近 2 在规则中建立全部过孔上涂漆的规则 方法是将其设置为-1 如果想保留一些测试用的点,可以选中这些过孔并override这些规则

布通之后,松了一口气,接下来调整和优化

地线铺通 添加过孔强化接地 检查安全间距 走线检查 美观 标号 过孔涂漆 solder mask expansion – via xxx,then -50mil 其他: 泪滴 板子号 mark点 检查过孔涂漆规则 检查主控芯片处的走线 电源走线的过孔大一些 元件排列整齐美观 考虑到检测时测试的需要,设置必要的测试点 有的固定焊盘加入地 mark 连接器引脚辅助标识 3MM 如果加不上,要求制作PCB加上贴片边 检查与原理图是否一致 重新导入网络表,看变化的有哪些 检查固定性位置有没有变化 检查接插件是否对应 检查三段器件封装是否对应 检查芯片有没有在操作过程中误水平垂翻转 DRC检查错过过多自动停止 有时显示检测出错误结果为零,结果并不是真的为零,而是违反规则过多超过了500个, 最后一次build覆铜版之前的工作 检查走线质量 放置Mark点 Mark点用于贴片时作为参考点 两个零过孔焊盘,正反面相摞 还是都放点,即便不使用贴片也没有关系 Mark点是用来光学定位确定平面的。这样说就很容易理解需要几个了吧?三点一面么~!对于大的PCB来说 三个点是必要的。另外一些特殊的元器件,比如很多PIN脚的高集成度芯片,为了保证焊接质量,也可以在其附近放一个Mark点来进行定位,一般不需要。 貌似两个就行,放多了mark点就是方便机器选取最合适的点,我们厂做板如果地方比较小都是放两个就OK 补泪滴 补泪滴在走线和焊盘直接有一个由细到粗的渐变,可以提高电路的可靠性 可采用22mil安全间距 具体操作是tools-teardrops 和覆铜板一样,补泪滴操作以前也一定要保证一个前提:要有一个合适的安全艰巨! 因为这是在规则下的自动操作,如果没有安全艰巨和过小,补泪滴后会严重影响安全性,有的或许已经短路 补泪滴可以选择采用弧形的补泪滴 覆铜之后补泪滴,可以把按大的安全间距覆铜一下然后泪滴,然后再重新覆铜

定型后的检查和完善

终于算竣工了,可以轻松地做一些轻松的工作 摆放标号 过孔涂漆和设置几个测试点 过孔涂漆有利于减少短路的可能性 设置让过孔上涂漆: 双击选中过孔,属性重选中tenting,然后全局 如果全局应用不成,在规则-制造中建立soldermask expansion中建立一个针对过孔的,然后expansion中输入一个负数值。右侧说明文字中有 为了让一些地露出用于做测试用,可以选中override忽略 防止板子标号 日期 螺丝孔从keepout层改过来 删除各个板最后的辅助线

PCB审核

检查原理图 检查布局 检查封装是否合适 插件 贴片 管脚对应 标识 空管脚 是不是没有连接起来 线粗细 安全间距 铺地效果是否好 电源线是否存在瓶颈 丝印

高速PCB设计和EMC专题

数字模拟分离 模拟部分 声音部分 包括从外部输入的音频信号,MIC输入 视频部分 包括视频变换电路,视频电源部分,字符叠加部分 数字部分 CPU周围和573控制信号部分 高速低速 高速部分 CPU时钟部分 485通讯信号 电源部分 高频考虑 石英晶体下面以及对噪声敏感的器件下面不要走线 减小环路面积 布线的时候要把高速线分配到靠近地平面的层,或者高速线旁边并行走一两条地线,起到屏蔽和就近提供回流的功能 模拟信号和数字信号都要回流到地,因为数字信号变化速度快,从而在数字地上引起的噪声就会很大,而模拟信号是需要一个干净的地参考工作的。如果模拟地和数字地混在一起,噪声就会影响到模拟信号。 一般来说,模拟地和数字地要分开处理,然后通过细的走线连在一起,或者单点接在一起。总的思想是尽量阻隔数字地上的噪声窜到模拟地上。当然这也不是非常严格的要求模拟地和数字地必须分开,如果模拟部分附近的数字地还是很干净的话可以合在一起。 模拟地线、数字地线等接往公共地线时要用高频扼流环节。或用单点接地。 不再严格根据功能划分,注重考虑模拟和数字部分的分开 不要让高频的数字信号影响视频模拟低频,所以VCC不能要单独引出不能从485处引过来

多层板设计专题

四层板设计 抗干扰 过孔多了,整个电路板的过孔分为三类,顶层到第一中间层的过孔,第二中间层到底层的过孔,顶层到底层的过孔。我在画顶层和第一中间层的线路时,想让界面只显示顶层到第一中间层的过孔和顶层到底层的过孔,隐藏第二中间层到底层的过孔,但不知如 何设置 放过孔后属性设置从什么层到什么层 从顶层到底层反而是最远的 电源层和地层需要覆铜,信号层还需要铺地了吗?不的话可能需要打很多过孔 常用四层板层叠方案

方案1为业界现行四层PCB主选层设置方案,在元件面下有一地平面,关键信号优选布TOP层; 为了达到一定屏蔽效果,有人试图把电源、地平面放在TOP、BOTTOM层,即采用方案2: 方案2为了达到想要屏蔽效果,至少存在以下缺陷: A、电源、地相距过远,电源平面阻抗较大 B、电源、地平面由于元件焊盘等影响,极不完整 C、由于参考面不完整,信号阻抗不连续 在当前大量采用表贴器件,且器件越来越密情况下,本方案电源、地几乎无法作为完整参考平面,预期屏蔽效果很难实现;方案2使用范围有限。但在个别单板中,方案2不失为最佳层设置方案。以下为方案2在XX产品接口滤波板中使用案例; 案例:在以太网交换机接口滤波板中,出现了以下情况: A,整板无电源平面; B,整板走线简单,但作为接口滤波板,布线辐射必须关注; C,该板贴片元件较少,多数为插件。 分析:1,由于该板无电源平面,电源地耦合无须考虑; 2,由于贴片元件少,若表层做平面层,内层走线,参考平面完整性基本 能得到保证,而且第二层可铺铜保证少量顶层走线参考平面; 3,作为接口滤波板,PCB布线辐射必须关注,若内层走线,表层为GND, 走线得到很好屏蔽,传输线辐射得到控制; 鉴于以上原因,在本板层排布时,我们决定采用方案2,即:GND、S1、S2、GND,由于表层仍有少量短走线,而底层则为完整地平面,我们在S1布线层铺铜,保证了表层走线参考平面; 列举以上特例,就是要告诉大家,要领会层排布原则,而非机械照搬。 方案3同方案1类似,适用于主要器件在BOTTOM布局或关键信号底层布线情况;一般情况下,限制使用此方案; ? 它中间不是覆铜板polygon plane了,而是internal plane,选择一个电气网络 外面的不用覆铜板铺地了?多打过孔 层堆栈管理器属性设置对话框右侧有一列层操作按钮,各个按钮的功能如下。 (1)AddLayer:添加中间信号层。例如,需要在GND和Power之间添加一个高速信号层,则应该首先选择GND层,如图11-6所示。单击AddLayer按钮,则会在GND层下添加一个信号层,如图11-7所示,其默认名称为MidLayer1,MidLayer2,?,依此类推。双击层的名称或者点击Properties按钮可以设置该层属性。 (2)AddPlane:添加内电层。添加方法与添加中间信号层相同。先选择需要添加的内电层的位置,然后单击该按钮,则在指定层的下方添加内电层,其默认名称为InternalPlane1,InternalPlane2,?,依此类推。双击层的名称或者点击Properties按钮可以设置该层属性。 (3)Delete:删除某个层。除了顶层和底层不能被删除,其他信号层和内电层均能够被删除,但是已经布线的中间信号层和已经被分割的内电层不能被删除。选择需要删除的层,单击该按钮,弹出如图11-8所示的对话框,单击Yes按钮则该层就被删除。 (4)MoveUp:上移一个层。选择需要上移的层(可以是信号层,也可以是内电层),单击该按钮,则该层会上移一层,但不会超过顶层。 (5)MoveDown:下移一个层。与MoveUp按钮相似,单击该按钮,则该层会下移一层,但不会超过底层。 (6)Properties:属性按钮。单击该按钮,弹出类似图11-3所示的层属性设置对话框。 Plane为负面,在Plane上的Track 为无铜区。 Layer为正面,在Layer上的Track 为有铜区。 都可以做为Ground,Plane可以自动通过VIA 或PAD 直接连到Plane.而Layer还要覆铜。 所以Ground一般用Plane. Plane专用作电源/地层,不能自由布线,自动产生连接;layer和top、bottom layer一样可以自由布线。 add plane是增加电源层和地层,而电源和地一般都会有多个,要进行分割,分割后的PLANE内部其实就是铺铜了,那是负片;add layer的话一般是用来增加信号层的。

PCB设计软件使用

Protel使用杂项

shift+s可快速切换查看单独一面的 如何翻转另一面? 有时发现打开pcb文件里面看不到内容,文件移动到桌面可以了,可能是开始文件路径太深了 protel缺点:走线等不太智能,常常要先删除线然后重新连接,没有自动的智能,麻烦;相比有些软件在这上面做的比较智能

Pads使用杂项

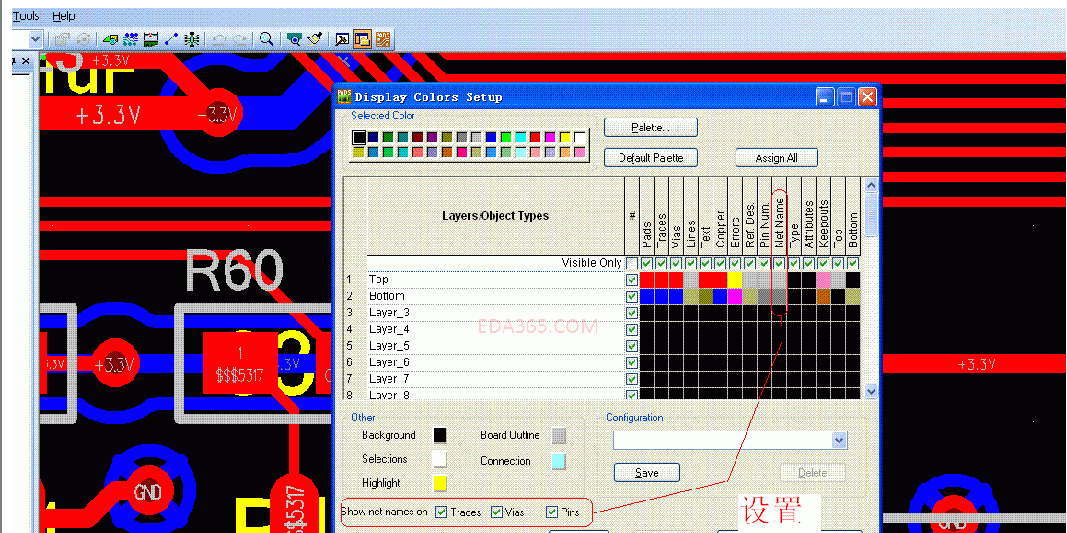

Mentor公司,Pads现在是新集合平台,包含了以前从Innoveda收购的powerpcb,现在成为Pads layout;另外包含了Pads Logic(PowerLogic)等 可以对付大多数的高速板 我把它称作低端中的无冕之王,它是我认为在所有低端的pcb软件中最优秀的一款 pads 9.2开始支持win7 9.2版本之前在pad、track上不能显示网络名称,只能在左下角看浮动显示,是一个缺陷,9.2版本加上这样功能了;display colors setup里面选中name names,并选择靠下面点的show net names on中的选项

格式

protel输出时 .pcb格式文件 pads输出.PCB格式,也可导出.asc格式的PCB asc格式 orcad可导出asc后缀的网络表,pads的Pcb也可导出asc格式的PCB pads打开asc格式PCB,导入 protel打开asc格式Pcb,直接open然后选择asc格式的,格式转化之后不能保证和原来一样

Altium使用

从protel99se到altium还是有不少地方需要学习和适应的 批量替换,protel99se中很方便,altium中的做法是,比如封装批量替换,选择similiar,然后在PCB inspector中填写新的封装名(新封装应该有才行) 将文档加入到项目中:file-new project 然后将free document移动过去 protel99se文件导入altium

前者为:导入时选择bunding rectancle作为边框 后者为:导入时选择keepout层元素作为边框 有时pcb查看整页面视图时候不居中 应该是文件中还有其他内容,比如打开覆铜别的地方有没有删除的覆铜

OrCAD layout转protel:

直接protel中导入(99se)或打开(dxp);或者layout中export按要求进行转换,需要先弄一个ASCII格式的PCB的 如何从layout转为protel 导入后需要自行修改的 似乎一些层太多了,protel中常用top bottom keepout multi topoverlay bottomoverlay 导入后过孔成了元件,重新添加过孔 重新删除和添加元器件 覆铜板边沿成了多余导线 有过孔放在焊盘上的现象 批量替换0805 该库中封装 两个机械层怎么处理 测试的PAD也成了元器件 为什么标号不和器件一起移动 原来标号转化为string了,自己的反而隐藏了

Protel导回Layout

Protel中到处ASCII 2.8格式,在Layout中导入,做一下层映射才好,结果证明:层对应的不好 protel转orcad layout的*.max文件我倒是试过,但反过来我从未成功过,不知可否告知你*作的protel版本? 还有一点,即使转换成功,还是要人为作很大的修改的(并不完全) 2007-11-16 20:30 xue 从Orcad Layout转到ProtelDXP时,为何过孔(Via)都变成了焊盘(Pad)? 如题:从Orcad Layout转到ProtelDXP时,为何过孔(Via)都变成了焊盘(Pad)?怎么样才能避免这样子哦?谢谢诸位观贴的兄台们。 2007-11-17 18:21 dht029

你好,对于这个问题,其实目前我也没有完整的答案,感觉是虽然各个EDA软件公司直接给对方做了接口但是对于Via和铺铜的处理仍然是个比较大的问题。主要是这两个数据各个公司采用的模式不同。所以一般的转换我们会删除铺铜并且对Via做检查的。同样的问题也出现在Allegro和Pads的转换。目前手上没有正版的ProtelDXP不能做测试,不好意思了。另外有一款叫CAMcad的PCB转换工具你可以试试,不错的

PowerPCB转到Protel

powerpcb导出选择ascii,然后选择v3.5格式,然后prote pcb文件中导入 DXP中直接打开ASC文件,会有一些不吻合原文件的地方,比如有的焊盘编程没有过孔的焊盘,有的连线似乎增加了泪滴导致间距变小

protel到powerpcb

Mentor Graphics公司(就是生产POWERPCB的公司,呵呵)提供有一个转换工具:Protel PCB to PADS Layout Translator

软件异常

{ protel access violation at address xxx Exception Infomation: Exception Occurred In PCB: ChangeObjectGraphically Ignore Quit 规则中取消选中一些规则也不行 preference 中取消Online DRC也不行 尝试用兼容方式运行该程序.右键点击图标——属性——兼容型——选中“以兼容方式运行该程序”——下面的选框中可以选择以95、98、NT4.0或2000模式来运行。推荐选择98试试看。 –>不行 是不是装了360?360会偷偷升级office里面一个文件,使protel不能用 出现的错误: 1. protel 99se 加载扩展名为DDB的库文件时出现”file is not recognized” 2. 新建项目文件时出现”Root has been deleted” 解决方法如下: 出现的原因是: 360为了修复一个OFFICE的溢出漏洞用了一种临时的解决方法,将一个可以访问access的ACTIVEX控件给反注_册掉了(msjtes40.dll) 解 决 方 法: 重新注_册一下这个dll文件,在”运行”里输入”regsvr32.exe msjtes40.dll”,然后点”确定”,出现注_册成功提示后即可解决问题. —>不行 右击“我的电脑”。单击“属性”。 在“系统属性”中单击“高级”。 在“性能”中单击“设置”。 在“性能选项”中单击“数据执行保护”。 单击“添加”。选择要运行的程序。 —>不行 以前我也遇到过,我当时怀疑是程序坏了,我删除后重新安装还是一样,后来把C盘残余的带有protel字样的文件全部删除,重新安装后OK —>不行 后来转成dxp在dxp中弄 }

制作和工艺相关

输出Gerber文件

转

cam350抓图 从实例认识gerber图层

gerber各层的含义 CAM350-file-import打开 Top Layer .GTL 顶层走线 *.GTL Bottom Layer .GBL 底层走线 *.GBL Top Overlay .GTO 顶层丝印 *.GTO Bottom Overlay .GBO 底层丝印 *.GB0 Top Paste .GTP 顶层表贴(做激光模板用) *.GTP Paste层就是锡膏层,用它来制作刷锡膏的钢网,这一层需要露出需要焊接的焊盘。 Bottom Paste .GBP 底层表贴(做激光模板用) *.GBP Top Solder .GTS 顶层阻焊(也叫防锡层,负片) *.GTS Solder(阻焊)层比Paste层稍微大一些,按照它来涂覆绿油等阻焊材料,露出焊盘,比焊盘稍大。有solder的地方露出铜皮。 Bottom Solder .GBS 底层阻焊(也叫防锡层,负片) *.GBS MidLayer1 .G1 内部走线层1 MidLayer2 .G2 内部走线层2 MidLayer3 .G3 内部走线层3 MidLayer4 .G4 内部走线层4 Internal Plane1 .GP1 内平面1(负片) Internal Plane2 .GP2 内平面2(负片) Mechanical1 .GM1机械层1 Mechanical2 .GM2 机械层2 Mechanical3 .GM3 机械层3 Mechanical4 .GM4 机械层4 其实板子的外边框应该用机械层,但是现在很多人都用keepout层,导致制版商都默认了 Keep Out Layer .GKO 禁止布线层(可做板子外形) *.GK0 keepout 只是禁止布线层,就是说信号线不能穿越它,不用它也是可以的,因为你手工布线,你不可能把线布到边框外边,所以就可以不用禁止布线层了。 铺地前可以用keepout线圈起不想布线的地方,记得要移走,否则制版的人会给你挖个洞 Top Pad Master.GPT 顶层主焊盘 *.GPT Bottom Pad Master .GPB 底层主焊盘 *.GPB Aperture Data.APR光圈文件 Drill Data .DRL 钻孔数据 Drill Position.TXT钻孔位置 Drill Tool size.DRR钻孔尺寸 Drill Report.LDP钻孔报告 == CAD文档一般指原始PCB设计文件,如protel、PADS等PCB设计文件,而用户或企业设计部门,往往出于各方面的考虑,只愿意提供给生产制造部门电路板的Gerber文件。 Gerber文件是所有电路设计软件都可以产生的文件,在电子组装行业又称为模版文件(stencil data),在PCB制造业又称为光绘文件。可以说Gerber文件是电子组装业中最通用最广泛的文件格式。 有了Gerber文件, 才可以去制作PCB, gerber文件体现了PCB各个线路层的布局, 包含丝印层, PAD位置等等相当信息.简而言之, Gerber文件就是其对应PCB的信息集合.

导出BOM

相比从原理图生成BOM,有时候从PCB生成BOM更直接,也方便和PCB核对,在我们实际工作中会比较有用,设计人员只需将PCB发给做BOM的即可 方法如下: 打开PCB,选择菜单File –》CAM Manager,然后按照向导操作,选择BOM,一步步操作下去到完成 选中生成的.cam文件,然后Tools –》Generate CAM File,则生成一个CAM for xxx目录,里面即为生成的BOM

导出丝印图

protel中print/preview产生PPC文件,可删除一些图层保留一些图层然后打印,打印PPC,insert printout insert print layers获得。底层丝印翻转过来了 如果丝印Gerber不导出,另外处装配图,如果能放的上的话,建议还是放上;如果另出装配图,位号比上次大些,上次的显得比较小

再了解层

topsolder开窗加锡的,但topaste 是用来做smt钢网的,贴片用的,不要搞混

PCB加工工艺了解

了解PCB加工工艺便于提高PCB设计质量 在设计PCB和打样过程中,和加工厂家也有一些沟通,从加工厂家那里获得一些反馈信息 按面积计费,同时都有工程费,几百块,比如三百到五百 板厚比如1.6mm 1mm,铜厚比如1oz=1.35mil=35um 是否含铅,国内无环境要求一般含铅便宜 油墨颜色比如绿色,丝印颜色 白色

Gerber生成错误

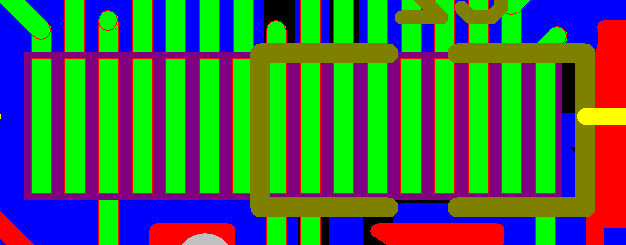

日期:2012-04-28 wo 15:04:43 在吗 贾 15:05:36 在 wo 15:08:12 集控开窗问题有回复了,厂商说是加工的问题。我们设备要走强电、大电流,没有开窗不涂锡的话,就不能走那么大电流,很有影响,看一下怎么处理吧 wo 15:11:46 在吗 贾 15:14:04 这个事情具体的我都不知道是什么情况 wo 15:15:24 发邮件我都转发到你邮件中了 wo 15:15:35 不清楚什么可以讲一下 贾 15:17:12 晚点在说吧,我这会有事在忙 wo 15:17:49 这个事情你要负责处理下的,目前投的板子都不能用,目前都加工了 wo 15:18:12 这是个比较重要和麻烦的事情 wo 15:18:56 真不行,要么换厂家呢 贾 15:20:33 那你和他们沟通的结果是你们做不了呢?还漏掉忘做了呢 wo 15:20:55 厂家已经确认,是他们加工的问题,不是设计的问题 wo 15:21:58 我手头事情很多,是要怎么处理麻烦你跟踪一下,看有没有补救办法 贾 15:22:00 这个我知道,关键是他们加工是不能做出来 ,还是忘了 wo 15:22:26 应该是忘了,PCB厂家都能做的 做了几百套了 带来了很多麻烦和损失 PCB方可以扣钱饿 自己通过刮铜皮涂锡或者焊线解决 Protel 99SE 输出的文件Protel DXP都能正确的打开,但是Protel 99SE就不能正确的显示Protel DXP的覆铜设置 后来还是承认他们加工有问题,但是也指出了设计文件也有问题,理解错了 经过再次学习和分析Gerber文件,发现确实少了solder层的元素 然后就考察生成gerber的方法 后来发现protel99se文件转换为dxp后就没有看到solder层 进一步发现,转化的封装是可以的,但为什么就显示不出来了 后来发现规则里面,SolderMaskExpansion中原来针对过孔的规则应用到all了 是protel99se文件转altium文件时,一个只应用于过孔的规则被应用到所有了 以后注意检查转化后的丢失情况,比如覆铜、规则

solder层过大

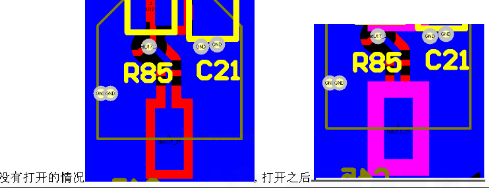

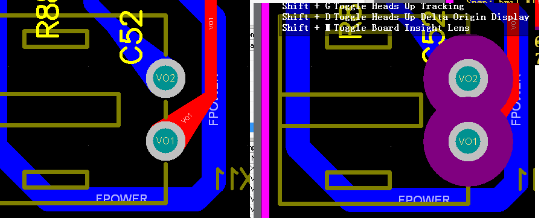

沿用以前的封装,而以前的封装本身有问题 以前也发现并纠正过一些 2011.12.26到现在已经多次遇到封装solder层过大的问题,审核别人设计的PCB时没有注意到 还是以前封装库里的封装,但是以前没有发现问题而后来不断出现,应该是以前的PCB加工厂家特殊处理了吧,但封装本身确定是有问题的 问题再现: solder层做的过大,超过了安全间距,跨接在相邻的其他地方去,容易导致短路 平常没有打开solder层没有注意到封装做的有问题

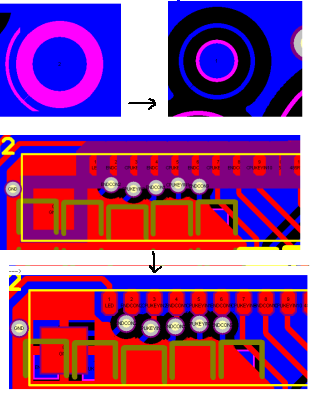

可以看到bottom solder层很大,超过了焊盘和铺地的安全间距,跨到铺地上去了,而铺地上有铜,正规做出来也会在铺地的地方露出铜皮的,这样焊接时候就容易短路 下面的top solder层做的过大

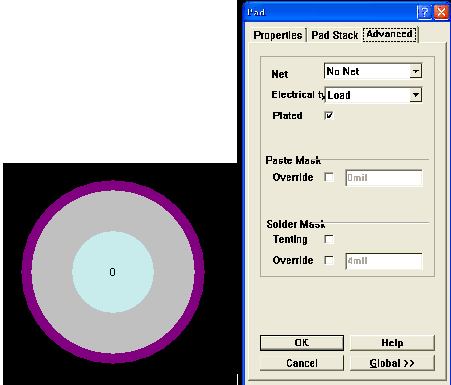

那么应该多大? 系统默认的焊盘中 solder层大了4mil,如果按10mil的安全间距,不会导致solder层过大

澄清solder层: 阻焊层就是solder mask,是指印刷电路板子上要上绿油的部分。实际上这阻焊层使用的是负片输出,所以在阻焊层的形状映射到板子上以后,并不是上了绿油阻焊,反而是露出了铜皮。 solder层要露出铜皮,还需要同时有top或bottom层的铜皮才行 像密集的CPU引脚处,虽然solder层连起来了,但是焊盘是隔离的,所以还不会连起来

另外,助焊层:paste mask,是机器贴片时要用的,是对应所有贴片元件的焊盘的,大小与toplayer/bottomlayer层一样,是用来开钢网漏锡用的。 下面案例中,根据加工厂家提出的情况,又做了修改

日期:2012-09-03 Flying 13:34:30 王工在吗? pcb 13:34:38 我是XX电子倪XX wo 13:34:55 你好! pcb 13:35:18 您等下,我把图片截给您看看 wo 13:35:28 好 pcb 13:35:35 pcb 13:36:33 就是这个MARK点导致了MARK点周围的铜箔漏出来了,我们要不要把铜箔修掉一点,保证不漏铜 wo 13:37:27 嗯,这个是大了,周围的割掉吧,不然搭到别的上面了 wo 13:37:42 或者我更新一下PCB也行 pcb 13:37:43 是切铜箔吧 pcb 13:37:52 您等下,还有一个另外的问题 wo 13:38:03 好 pcb 13:39:11 pcb 13:39:55 这个位置的打开也是好大,是不是需要修改,我给您电话 wo 13:40:16 这个是哪个地方大? pcb 13:46:23 pcb 13:50:26 pcb 13:54:10 pcb 13:54:48 pcb 14:44:37 王工,资料修改好了吗 wo 14:54:20 在吗 pcb 14:54:56 在的 wo 14:55:09 请先看下改后的是否可以 pcb 14:55:32 能用这个做板子吗 14:55:35 成功发送文件“草稿.rar”(150.00KB) 打开文件 打开所在文件夹 wo 14:56:13 这个先请看下有没有毛病,如果没有改的再重新发下压缩包 pcb 14:56:27 pcb 15:01:41 可以,是这样子的 wo 15:01:51 好的 pcb 15:02:40 后续在那种大铜面里面的可以不加那个保护环,只有那种独立的MARK点需要加,那种在大铜面里的,不加也是没有影响的 wo 15:02:59 好的 pcb 15:03:17 你把文件给到贾小姐吧,我这边今天安排生产 wo 15:03:29 好的,我发给她 pcb 15:03:52 谢谢了,等板子做好了,我到时带板子一起过去拜访您 wo 15:04:09 好,谢谢 pcb 15:04:22 没有,大家一起把事情做好

PCB设计中割断开槽宽度问题

尤其强电PCB设计时,有时为了增加两条走线或者走线与器件之间的爬电间距,会遇到割断PCB开槽的问题 据和厂家沟通,这样的槽不要多开,会增加PCB制作成本 宽度问题:最好达到1mm { 2013.05.20 XXX 16:40:18 在吗,咨询个技术问题:PCB板上开孔或割槽最窄可以多少? 典XXX 16:41:34 金属槽还是非金属的 (来自微信: http://weixin.qq.com/q ) XXX 16:42:09 非金属的,直接割掉的那种 两条线之间割开,增加爬电间距的 典XXX 16:44:42 Cnc铣出来是0,6mm,电脑钻是0,5mm XXX 16:45:56 好,谢谢 典XXX 16:45:57 最好是铣出来,成本低些,这种槽不要弄的太多了,成本高 典XXX 16:51:01 小的槽,铣刀容易断,一次也铣不了那么多块 XXX 16:51:15 0.7呢 典XXX 16:51:54 线到槽的距离只要有0,2mm就够了的 典XXX 16:53:45 就是线边的距离到槽边的距离只需要保证有0.2mm,我们就能保证不会伤到线的 我给你电话吧 XXX 16:54:11 哦,这样子,知道了 XXX 16:54:53 做到1mm个别地方有点难 典XXX 16:55:05 那就做0.9MM怎么样 如果没有特别的要求,这种槽尽量做大点,要不到时你们的成本会偏高的 XXX 16:55:43 好的,我知道了 谢谢 典XXX 16:56:19 线和线之间的距离看看能不能适当的做小点 典XXX 17:00:02 为了把槽做大点,在不影响功能的前提下 XXX 17:00:13 了解了 }

微隔线

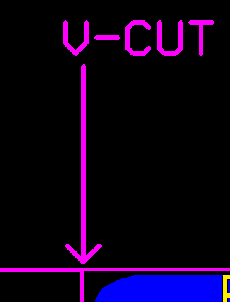

有时候需要某个地方割虚线,用手可以扳开的那种,如何标示呢? –>在需要微割的地方标明V-CUT就可以了,如下图,一般用KeepOut层

感悟

本人习惯根据PCB布板的方便调整CPU的引脚;而像原理图和PCB设计人员不同的情况,就不容易实现这种方便 没有调试的人画PCB,就不会千方百计为调试和质量考虑

杂烩

(Protel99se)由PCB器件生产lib然后更新到PCB时候要小心,这一操作过程未必完全符合期望,自己曾经对一块板子如此操作,但导致结构性定位好的 插针位置产生细微偏差,整个器件坐标没有变化,但是pad坐标发生了变化,经过比较,所有焊盘都x减去0.4mil、y减去0.6mil,虽然这样的误差几乎可以忽略,但是提醒自己还是要注意,避免这样操作 选择Push Obstacle模式可以在不满足安全间距的地方也走线,不用临时更改安全间距 空间十分有限的板子,也可将位号作为单独层导出